|

Размер: 13582

Комментарий:

|

Размер: 24085

Комментарий:

|

| Удаления помечены так. | Добавления помечены так. |

| Строка 60: | Строка 60: |

| === Intel *86 === | === Intel x86* === |

| Строка 64: | Строка 64: |

| Архитектура х86_64 является примером CISC-архитектуры (Complex Instruction Set Computer – компьютер с полным набором команд). В отличие от команд в RISC-архитектурах, таких как MIPS, каждая CISC-команда способна произвести больше работы. Из-за этого программы для CISC-архитектур обычно состоят из меньшего количества команд. Кодировки команд были подобраны так, чтобы обеспечивать наибольшую компактность кода – это требовалось в те времена, когда стоимость оперативной памяти было гораздо выше, чем сейчас. Команды имеют переменную длину, которая зачастую меньше 32 бит. Недостаток же состоит в том, что сложные команды трудно дешифровать, к тому же они, как правило, работают медленнее. Табл. Основные отличия между MIPS и x86_64 ||Характеристики|| MIPS|| x86_64|| ||Количество регистров||32, общего назначения|| 16, некоторые ограничения по использованию|| ||Количество операндов||3 (2 источника, 1 назначение)|| 2 (1 источник, 1 источник/назначение)|| ||Расположение операндов|| Регистры или непосредственные операнды || Регистры, непосредственные операнды или память|| ||Размер операнда || 32 бита|| 8, 16, 32 или 64 бита|| ||Коды условий|| Нет|| Да|| ||Типы команд|| Простые|| Простые и сложные|| ||Размер команд|| Фиксированный, 4 байта|| Переменный, 1–16 байтов|| Регистры: 64-разрядные RAX, RBX, RCX, RDX, RSI, RDI, RSP, RBP и R8,R9,...,R15; 32-разрядные ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, ESP, EBP; R8D-R15D являются младшими половинами 64-разрядных регистров; 16-разрядные АХ, ВХ, CX, DX, SI, DI, SP, BP, R8W -R15W явля ются младшими частями 32-разрядных регистров; 8-битные регистры АН, ВН, СН, DH и AL, BL, CL, DL, SIL, DIL, SPL, BPL, R8L-R15L - старшие и младшие части 16-битных регистров соответственно; Эти шестнадцать регистров можно, за некоторым исключением, считать регистрами общего назначения. Некоторые команды не могут использовать некоторые из них. Другие команды всегда записывают результат в определенные регистры. Регистр RSP, как правило, используется как указатель стека. Счетчик команд в архитектуре х86 называется RIP (instruction pointer). Он увеличивается при переходе от одной команды к другой, а также может быть изменен командами ветвлений, безусловных переходов и вызова процедур. Доступ к 64-битным регистрам и новым регистрам осуществляется через специальный REX-префикс. Таким образом, все опкоды команд, которые работают с 64-битными регистрами, увеличиваются в размере как минимум на 1 байт, и возникает серьёзная проблема оптимизации кода. Поэтому рекомендуется везде, где возможно, использовать 32-битные регистры. Команды х86_64 содержат только два операнда: операнд-источник и операнд-источник/назначение. Следовательно, команда х86 всегда записывает результат на место одного из операндов. Табл. Расположение операндов ||Источник/Назначение||Источник|| Пример|| Выполняемая функция|| ||Регистр|| Регистр|| add EAX, EBX|| EAX <– EAX + EBX|| ||Непосредственный операнд||Регистр|| add EAX, 42|| EAX <– EAX + 42|| ||Регистр|| Память|| add EAX, [20]|| EAX <– EAX + Mem[20]|| ||Память|| Регистр|| add [20], EAX|| Mem[20] <- Mem[20] + EAX|| ||Непосредственный операнд||Память|| add [20], 42|| Mem[20] <- Mem[20] + 42|| Возможны любые комбинации, ''исключая память–память''. В то время как MIPS всегда оперирует с 32-битными словами данных, команды х86 могут использовать 8-, 16- 32- или 64-битные данные.В 64-битном режиме размер адреса по умолчанию равен 8 байтам, размер операнда по умолчанию равен 4 байтам Архитектура х86 имеет 64-битное( на самом деле 48-битное) пространство памяти с побайтовой адресацией. х86 поддерживает много режимов адресации памяти. Расположение ячейки памяти задается при помощи комбинации регистра базового адреса, смещения и регистра масштабируемого индекса. Табл. Режимы адресации памяти || Пример|| Назначение|| Комментарий|| ||add EAX, [20]|| EAX <– EAX + Mem[20]||Смещение (displacement)|| ||add EAX, [ESP]|| EAX <– EAX + Mem[ESP]|| Базовая адресация|| ||add EAX, [EDX+40]|| EAX <– EAX + Mem[EDX+40]||Базовая адресация + смещение|| ||add EAX, [60+EDI*4]|| EAX <– EAX + Mem[60+EDI*4]||Смещение + масштабируемый индекс|| ||add EAX, [EDX+80+EDI*2]|| EAX <– EAX + смещение + Mem[EDX+80+EDI*2]||Базовая адресация + масштабируемый индекс|| Смещение может иметь 8-, 16- или 32-битное значение. Регистр масштабируемого индекса может быть умножен на 1, 2, 4 или 8. Режим базовой адресации со смещением аналогичен режиму относительной адресации в MIPS, используемому для команд загрузки и сохранения. Масштабируемый индекс обеспечивает простой способ доступа к массивам и структурам с 2-, 4- или 8-байтовыми элементами без необходимости использовать команды для явного расчета адресов. В 64-битном режиме введён режим адресации относительно RIP. В случае адре сации относительно RIP используются не 64-битные адреса данных и переходов, а 32-битные. Таким образом, можно достигнуть почти 40%-ного уменьшения раз мера кода. Флаги состояния Другие особенности х86: *Сегменты *Порты * команды, работающие с цепочками (последовательностями или строками) байтов или слов. Эти команды реализуют операции копирования, сравнения и поиска определенного значения. В современных процессорах такие команды, как правило, работают медленнее, чем последовательность простых команд, делающих то же самое, поэтому их лучше избегать. *префиксы - используются для изменения размера операндов, захвата внешней шины , предсказания ветвлений или повторения команды при обработке цепочки байтов или слов. Архитектуры x86* – это мешанина из всевозможных решений и функциональности, накопленных за годы разработки. Некоторые из них давно не несут никакой пользы, но приходится сохранять их для обратной совместимости со старыми программами. У этой архитектуры слишком мало регистров, ее команды сложно дешифровать, а набор команд трудно объяснить. Несмотря на эти недостатки, x86 остается доминирующей архитектурой для персональных компьютеров потому, что невозможно переоценить важность совместимости программного обеспечения, и потому, что огромный рынок оправдывает затраты на разработку все более быстрых x86-совместимых микропроцессоров. |

Обзор архитектур современных ЭВМ

ARM

- Инструкции ARM(Паттерсон)

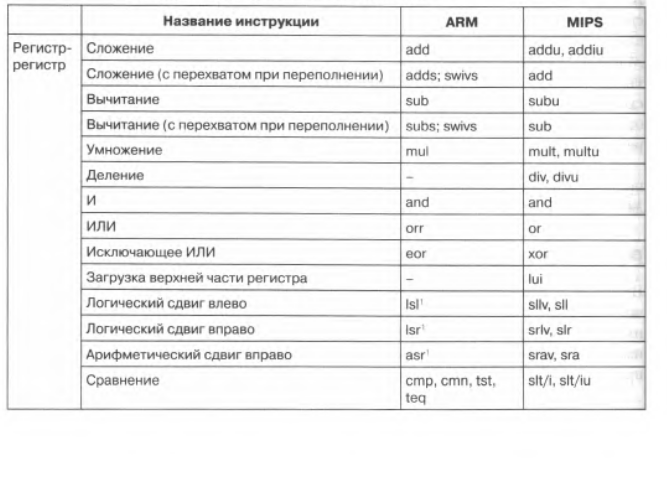

- ARM является наиболее популярной архитектурой набора инструкций для встроенных устройств и используется на более чем трех миллиардах производимых за каждый год устройств. Изначально предназначенная для системы Acorn RISC Machine, название которой позднее изменилось на Advanced RISC Machine, apхитектура ARM появилась в том же году, что и архитектура MIPS, и следовала схожим принципам. Все совпадения перечислены в табл. 2.11. Принципиальное отличие заключалось в том, что у MIPS больше регистров, а у ARM — больше режимов адресации. Табл. 2.11 Сходство наборов инструкций ARM и MIPS Как показано в табл. 2.12. для MIPS и для ARM использовались похожие основные наборы арифметическо-логических инструкций и инструкций переноса данных.

ARM

MIPS

год представления

1985

1985

размер инструкции

32

32

размер адресного пространства

32, плоское

32, плоское

выравнивание данных

да

да

модели адресации данных

9

3

целочисленные регистроы

16 GPO регистров, по 32 бита

31 GPO регистров, по 32 бита

ввод-вывод

с отображением на память

с отображением на память

Таблица 2.12. ARM-инструкции типа регистр-регистр и инструкции переноса данных, эквивалентные основным инструкциям MIPS. прочерки означают, что операция в этой архитектуре недоступна или не синтезирована в виде нескольких инструкций. Если имеется сразу несколько инструкций, эквивалентных основным инструкциям MIPS, они разделены запятыми. Сдвиги в ARM включены в виде части каждой инструкции обработки данных, поэтому сдвиги c верхним индексом 1 являются всего лишь разновидностью инструкции move. например lsг‘. Заметьте. что в ARM нет инструкции деления

Таблица 2.12. ARM-инструкции типа регистр-регистр и инструкции переноса данных, эквивалентные основным инструкциям MIPS. прочерки означают, что операция в этой архитектуре недоступна или не синтезирована в виде нескольких инструкций. Если имеется сразу несколько инструкций, эквивалентных основным инструкциям MIPS, они разделены запятыми. Сдвиги в ARM включены в виде части каждой инструкции обработки данных, поэтому сдвиги c верхним индексом 1 являются всего лишь разновидностью инструкции move. например lsг‘. Заметьте. что в ARM нет инструкции деления

- ARM является наиболее популярной архитектурой набора инструкций для встроенных устройств и используется на более чем трех миллиардах производимых за каждый год устройств. Изначально предназначенная для системы Acorn RISC Machine, название которой позднее изменилось на Advanced RISC Machine, apхитектура ARM появилась в том же году, что и архитектура MIPS, и следовала схожим принципам. Все совпадения перечислены в табл. 2.11. Принципиальное отличие заключалось в том, что у MIPS больше регистров, а у ARM — больше режимов адресации. Табл. 2.11 Сходство наборов инструкций ARM и MIPS

- Режимы адресации.

- B табл. 2.13 показаны режимы адресации данных, поддерживаемые в ARM. B отличие от MIPS ARM не выделяет регистр для содержания нулевого начения. В MIPS имеется всего три простых режима адресации данных (см. рис. 2.12), a вот у ARM имеется девять режимов, которые включают довольно сложные вычисления. Haпример, в ARM имеется режим адресации, который для формирования адреса может сдвигать значение одного регистра на любое количество позиций, добавлять его к значениям других регистров, а затем обновлять значение одного из регистров, присваивая ему значение полученного нового адреса. табл. 2.13 Таблица 2.13. Сводка режимов адресации данных. В ARM имеются отдельные режимы косвенной регистровой адресации и адресации «регистр + смещение», простое помещения нуля в смещение во втором режиме не используется, чтобы получить более широкий диапазон адресации, ARM сдвигает смещение на один или два разряда влево, если размер данных составляет полуслове или слово

Режим адресации

ARM v.4

MIPS

регистровый

+

+

непосредственный

+

+

регистр + смещение( побазе)

+

+

регистр + регистр(индексированный)

+

-

регистр + маштабированныйрегистр(маштабированный)

+

-

регистр + смещение и обновление регистра

+

-

регистр + регистр и обновление регистра

+

-

автоинкрементный,автодэкрементный

+

-

относительный по PC

+

-

- B табл. 2.13 показаны режимы адресации данных, поддерживаемые в ARM. B отличие от MIPS ARM не выделяет регистр для содержания нулевого начения. В MIPS имеется всего три простых режима адресации данных (см. рис. 2.12), a вот у ARM имеется девять режимов, которые включают довольно сложные вычисления. Haпример, в ARM имеется режим адресации, который для формирования адреса может сдвигать значение одного регистра на любое количество позиций, добавлять его к значениям других регистров, а затем обновлять значение одного из регистров, присваивая ему значение полученного нового адреса. табл. 2.13

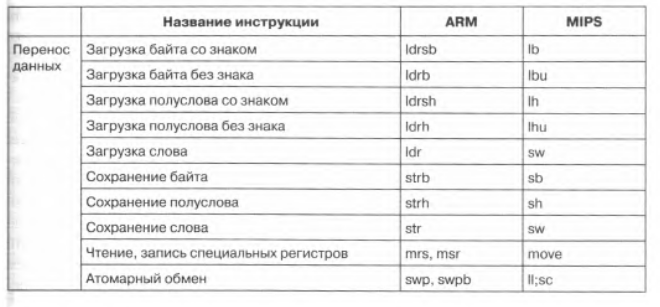

- Сравнение и условный переход

- B MIPS для вычисления условий переходов используется содержимое регистров. В ARM используются традиционные четыре разряда кода условия, сохраняемые в слове состояния программы: отрицательный, нулевой, переноса и переполнения - negative, zero. carry и overflow. Они могут устанавливаться при выполнении любой арифметической или логической инструкции; в отличие от более ранних архитектур эта установка для каждой инструкции является выборочной. Явный выбор создает меньше проблем при конвейерной реализации. В ARM используются условные переходы для проверки кодов условий, чтобы определить все знаковые и беззнаковые соответствия. Инструкция сравнения - CMP вычитает один операнд из другою. а пo разнице устанавливает коды условия. Инструкция отрицательного сравнения — compare-negative (CMN) — прибавляет один операнд к другому, а по сумме устанавливает коды условий. Инструкция ТSТ выполняет логическое И двух операндов для установки всех кодов условий, кроме переполнения - overflow, а инструкция TEQ использует исключающее ИЛИ для установки значений первых трех кодов условий. Одно из необычных свойств ARM заключается в том. что каждая инструкция имеет настройку на условное выполнение в зависимости от кодов условий. Каждая инструкция начинается с четырехразрядного поля. определяющего, будет ли она работать как холостая инструкция — no operation instruction (nop) — или как настоящая инструкция, в зависимости от кодов условий. Следовательно, по сути условные переходы рассматриваются как условное выполнение инструкции безусловного перехода. Условное вы волнение позволяет избежать перехода путем обхода его инструкции. На простое условное выполнение одной инструкции требуется меньше времени и пространства для кода. На рис. 2.16 показаны форматы инструкций для ARM и MIPS. Принципиальная разница заключается в четырехразрядном поле условного выполнения в каждой инструкции и меньшем по размеру поле регистра, потому что во ARM используется в два раза меньше регистров.

Рис. 2.16. Форматы инструкций ARM и MIPS. Разница заключается в том, что в одной архитектуре 16. а в другой 32 регистра

Рис. 2.16. Форматы инструкций ARM и MIPS. Разница заключается в том, что в одной архитектуре 16. а в другой 32 регистра

- Уникальные характеристики ARM

- B табл. 2.14 показаны несколько арнфметическо-логических инструкций. отсутствующих в MIPS. За неимением специально выделенного регистра, содержащего нуль. в этой архитектуре есть отдельные коды для выполнения тех операций, которые в MIPS реализуются с помощью регистра $zero. Кроме того, в ARM имеется поддержка для арифметики, оперирующей несколькими словами. Поле непосредственного значения ARM. состоящее из 12 разрядов, имеет новую интерпретацию. Восемь самых младших разрядов расширяются нулями до 32-разрядного значения, затем прокручиваются вправо на количество разрядов, указанное в первых четырех разрядах поля и умноженное на два. Одно из преимуществ заключается в том, что такая схема может представить все степени двойки в 32-разрядном слове. Было бы интересно исследовать вопрос, позволяет ли такое разделение охватить больше непосредственных значений, чем простое 12-разрядное поле. Операнд, подвергающийся сдвигу, не ограничивается непосредственными значениями. У второю регистра всех арифметических и логических операций по обработке данных есть возможность подвергнуться сдвигу еще до того, как он будет использован в операции. вариантами сдвига являются логический сдвиг влево, логический сдвиг вправо, арифметический сдвиг вправо и вращение вправо.

Таблица: 2.14. Арифметические и логические инструкции ARM. отсутствующее в MIPS

- В ARM также имеются инструкции для сохранения групп регистров. называемые блочными загрузками и сохранениями. Под управлением 16-разрядной маски внутри инструкций любой из 16 регистров может быть загружен из памяти или сохранен в ней с помощью одной инструкции. Эти инструкции могут сохранять и восстанавливать регистры при входе в процедуру и при возвращении из нее. Эти инструкции могут также использоваться для блочного копирования памяти, и сегодня блочное копирование приобретает все больший вес при их использование.

- B табл. 2.14 показаны несколько арнфметическо-логических инструкций. отсутствующих в MIPS. За неимением специально выделенного регистра, содержащего нуль. в этой архитектуре есть отдельные коды для выполнения тех операций, которые в MIPS реализуются с помощью регистра $zero. Кроме того, в ARM имеется поддержка для арифметики, оперирующей несколькими словами. Поле непосредственного значения ARM. состоящее из 12 разрядов, имеет новую интерпретацию. Восемь самых младших разрядов расширяются нулями до 32-разрядного значения, затем прокручиваются вправо на количество разрядов, указанное в первых четырех разрядах поля и умноженное на два. Одно из преимуществ заключается в том, что такая схема может представить все степени двойки в 32-разрядном слове. Было бы интересно исследовать вопрос, позволяет ли такое разделение охватить больше непосредственных значений, чем простое 12-разрядное поле. Операнд, подвергающийся сдвигу, не ограничивается непосредственными значениями. У второю регистра всех арифметических и логических операций по обработке данных есть возможность подвергнуться сдвигу еще до того, как он будет использован в операции. вариантами сдвига являются логический сдвиг влево, логический сдвиг вправо, арифметический сдвиг вправо и вращение вправо.

Приложение ARM от Таненбаума ARM_Tan.pdf

Intel x86*

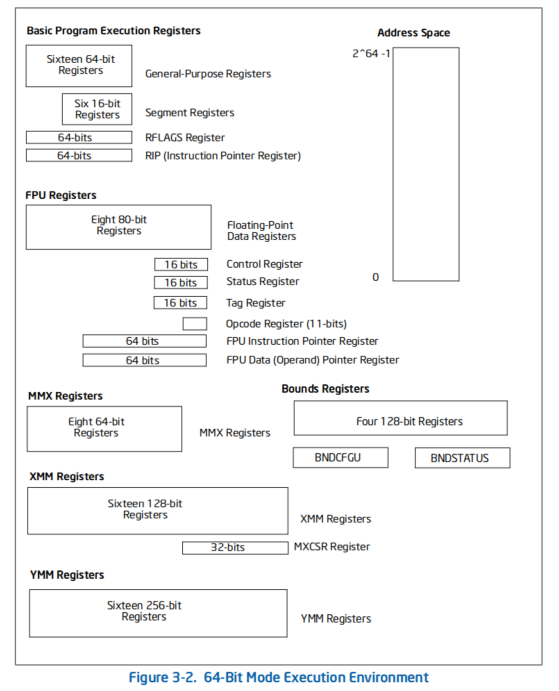

Современные процессоры Intel64 поддерживают множество режимов работы мы рассмотрим x86_64 Руководства для разработчиков приложений для 64- и 32-разрядных архитектур Intel®

- Архитектура х86_64 является примером CISC-архитектуры (Complex Instruction Set Computer – компьютер с полным набором команд). В отличие от команд в RISC-архитектурах, таких как MIPS, каждая CISC-команда способна произвести больше работы. Из-за этого программы для CISC-архитектур обычно состоят из меньшего количества команд. Кодировки команд были подобраны так, чтобы обеспечивать наибольшую компактность кода – это требовалось в те времена, когда стоимость оперативной памяти было гораздо выше, чем сейчас. Команды имеют переменную длину, которая зачастую меньше 32 бит. Недостаток же состоит в том, что сложные команды трудно дешифровать, к тому же они, как правило, работают медленнее.

Табл. Основные отличия между MIPS и x86_64

Характеристики |

MIPS |

x86_64 |

Количество регистров |

32, общего назначения |

16, некоторые ограничения по использованию |

Количество операндов |

3 (2 источника, 1 назначение) |

2 (1 источник, 1 источник/назначение) |

Расположение операндов |

Регистры или непосредственные операнды |

Регистры, непосредственные операнды или память |

Размер операнда |

32 бита |

8, 16, 32 или 64 бита |

Коды условий |

Нет |

Да |

Типы команд |

Простые |

Простые и сложные |

Размер команд |

Фиксированный, 4 байта |

Переменный, 1–16 байтов |

Регистры: 64-разрядные RAX, RBX, RCX, RDX, RSI, RDI, RSP, RBP и R8,R9,...,R15; 32-разрядные ЕАХ, ЕВХ, ЕСХ, EDX, ESI, EDI, ESP, EBP; R8D-R15D являются младшими половинами 64-разрядных регистров; 16-разрядные АХ, ВХ, CX, DX, SI, DI, SP, BP, R8W -R15W явля ются младшими частями 32-разрядных регистров; 8-битные регистры АН, ВН, СН, DH и AL, BL, CL, DL, SIL, DIL, SPL, BPL, R8L-R15L - старшие и младшие части 16-битных регистров соответственно;

- Эти шестнадцать регистров можно, за некоторым исключением, считать регистрами общего назначения. Некоторые команды не могут использовать некоторые из них. Другие команды всегда записывают результат в определенные регистры. Регистр RSP, как правило, используется как указатель стека.

- Счетчик команд в архитектуре х86 называется RIP (instruction pointer). Он увеличивается при переходе от одной команды к другой, а также может быть изменен командами ветвлений, безусловных переходов и вызова процедур. Доступ к 64-битным регистрам и новым регистрам осуществляется через специальный REX-префикс. Таким образом, все опкоды команд, которые работают с 64-битными регистрами, увеличиваются в размере как минимум на 1 байт, и возникает серьёзная проблема оптимизации кода. Поэтому рекомендуется везде, где возможно, использовать 32-битные регистры.

Команды х86_64 содержат только два операнда: операнд-источник и операнд-источник/назначение. Следовательно, команда х86 всегда записывает результат на место одного из операндов.

Табл. Расположение операндов

Источник/Назначение |

Источник |

Пример |

Выполняемая функция |

Регистр |

Регистр |

add EAX, EBX |

EAX <– EAX + EBX |

Непосредственный операнд |

Регистр |

add EAX, 42 |

EAX <– EAX + 42 |

Регистр |

Память |

add EAX, [20] |

EAX <– EAX + Mem[20] |

Память |

Регистр |

add [20], EAX |

Mem[20] <- Mem[20] + EAX |

Непосредственный операнд |

Память |

add [20], 42 |

Mem[20] <- Mem[20] + 42 |

Возможны любые комбинации, исключая память–память. В то время как MIPS всегда оперирует с 32-битными словами данных, команды х86 могут использовать 8-, 16- 32- или 64-битные данные.В 64-битном режиме размер адреса по умолчанию равен 8 байтам, размер операнда по умолчанию равен 4 байтам Архитектура х86 имеет 64-битное( на самом деле 48-битное) пространство памяти с побайтовой адресацией. х86 поддерживает много режимов адресации памяти. Расположение ячейки памяти задается при помощи комбинации регистра базового адреса, смещения и регистра масштабируемого индекса. Табл. Режимы адресации памяти

Пример |

Назначение |

Комментарий |

add EAX, [20] |

EAX <– EAX + Mem[20] |

Смещение (displacement) |

add EAX, [ESP] |

EAX <– EAX + Mem[ESP] |

Базовая адресация |

add EAX, [EDX+40] |

EAX <– EAX + Mem[EDX+40] |

Базовая адресация + смещение |

add EAX, [60+EDI*4] |

EAX <– EAX + Mem[60+EDI*4] |

Смещение + масштабируемый индекс |

add EAX, [EDX+80+EDI*2] |

EAX <– EAX + смещение + Mem[EDX+80+EDI*2] |

Базовая адресация + масштабируемый индекс |

- Смещение может иметь 8-, 16- или 32-битное значение. Регистр

масштабируемого индекса может быть умножен на 1, 2, 4 или 8. Режим базовой адресации со смещением аналогичен режиму относительной адресации в MIPS, используемому для команд загрузки и сохранения. Масштабируемый индекс обеспечивает простой способ доступа к массивам и структурам с 2-, 4- или 8-байтовыми элементами без необходимости использовать команды для явного расчета адресов.

В 64-битном режиме введён режим адресации относительно RIP. В случае адре сации относительно RIP используются не 64-битные адреса данных и переходов, а 32-битные. Таким образом, можно достигнуть почти 40%-ного уменьшения раз мера кода.

Флаги состояния

- Другие особенности х86:

- Сегменты

- Порты

- команды, работающие с цепочками (последовательностями или строками) байтов или слов. Эти команды реализуют операции копирования, сравнения и поиска определенного значения. В современных процессорах такие команды, как правило, работают медленнее, чем последовательность простых команд, делающих то же самое, поэтому их лучше избегать.

- префиксы - используются для изменения размера операндов, захвата внешней шины , предсказания ветвлений или повторения команды при обработке цепочки байтов или слов.

обеспечения, и потому, что огромный рынок оправдывает затраты на разработку все более быстрых x86-совместимых микропроцессоров.