06. Multitasking

(previous topic chore: how does cache strategies works anyway?)

- The task of multitasking

Effectively run a number of tasks over a certain time period

Rationale:

- Long-running I/O operations not using CPU vs. fast-running CPU mundane calculations

Slow human recognition (no difference between 1 ms and 1 µs)

Problems:

- Task alternation:

- timer interrupt

- context switch (registers, including PC and flags)

- Software vs. hardware

⇒ another task, the scheduler

- Task memory protection

- Software (any memory access wraps to grant subroutine)

- Hardware (tagged memory and code)

- Topological (address translation). E. g. forced indirect 24-bit addressing over special register with 32-bit address space (IBM PC i286).

- Overcommit

- Delayed memory provisioning (OS feature)

- Swapping/paging (OS + hardware)

Less evident problems:

- Cache inefficiency

- A number of hot areas

- Overall size

- ⇒ direct or associative?

⇒ both

L1 and L2

L1 and L2 (also: different .text and.data caches)

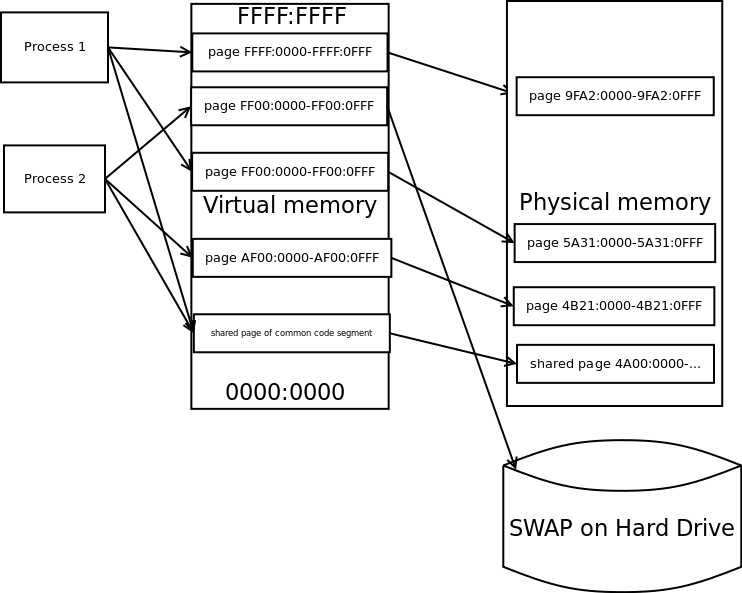

Virtual memory

- Virtual memory

mapping single continuous 0…LIMIT memory of each process to the real physical memory. See Virtual memory

Features:

Usually hardware (see Translation_lookaside_buffer)

- ⇒ TLB needs caching too

Performed by pages (small page — large TLB, large page — more overhead)

- Better to be accessible only by kernel

CPU supervisor mode

Swapping

- Paging

keeping and (some/LRU/excessive) memory pages on disk and restoring it on demand

- Swapping

keeping (LRU/excessive) full process memory on disk

Problems:

- Overcommit (HDD is LARGE)

Spatial locality in charge

Hardware implementation: so called page faults

Multicore

Practical: it's easy to insert another CPU (and redesign system board), rather then develop a new processor, that is two times faster

But:

Parallel asynchronous memory access ⇒ Cache_coherence

- A set of problems: ordering, propagation, informing, bald devil, ...

- ⇒ L3 cache (L1/L2 are usually core-specific)

Too many cores: Non-uniform_memory_access

- …

Modern processors are all multi-core (many cores on one chip).

Virtualization

Practical: run a number of operating systems on one computer

⇒ run a number of isolated supervisor mode processes (usually OS kernels)

- ⇒ allow each kernel to manipulate it's own TLB

- ⇒ create 3-level hierarchy

- hypervisor mode (may be one of kernels or special hyperkernel) can create, run and manage

- kernels in supervisor mode

- subsequent processes

- Provide environment isolation

Hardware requirements